AI数据中心的大脑

市场动态、竞争格局与投资主题分析备忘录

1.0 战略重心转移:人工智能时代下的内存新范式

生成式人工智能的崛起正在深刻重塑计算系统的经济版图。以往,系统的瓶颈主要在于纯粹的算力;而今,经济重心已然转移至受带宽和功耗双重制约的内存子系统。

这一根本性转变极大地提升了高带宽内存(HBM)、先进封装技术以及高性能服务器内存在整个产业链中的战略重要性。在当前以加速器为核心的数据中心架构中,内存子系统的性能和供应能力已成为决定AI应用规模和成本效益的关键因素。

现代计算系统中的内存并非单一产品,而是一个由不同技术构成的紧密耦合的层次结构。每一层都在物理实现、性能权衡(带宽、密度、延迟)及系统集成模式上存在显著差异。

理解这一层次结构对于分析AI硬件市场至关重要:

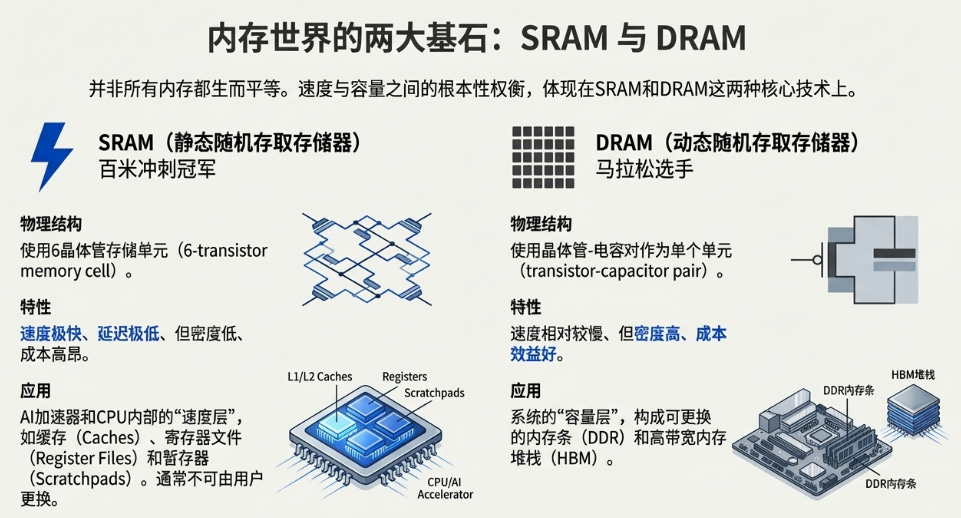

SRAM(静态随机存取存储器):作为“片上高速层”,SRAM通常由6个晶体管构成一个存储单元,被部署在CPU或GPU芯片内部,用作寄存器、高速缓存和暂存器等需要极低延迟的结构。由于其面积成本高、密度低,SRAM通常不作为用户可更换的独立组件。在AI系统中,它是确保核心计算单元能以最高速度获取数据的关键。

DRAM(动态随机存取存储器):作为“片外容量层”,DRAM采用“晶体管+电容”的单元结构,实现了更高的存储密度和更低的单位比特成本,尽管其速度慢于SRAM。这使其成为主导用户可更换内存模组(如服务器中的DIMM)和高密度片上集成内存的主流技术。在AI架构中,DRAM扮演着双重角色:

传统系统内存 (DDR):以DIMM模组形式存在,为主机CPU提供大容量的数据暂存和预处理空间。

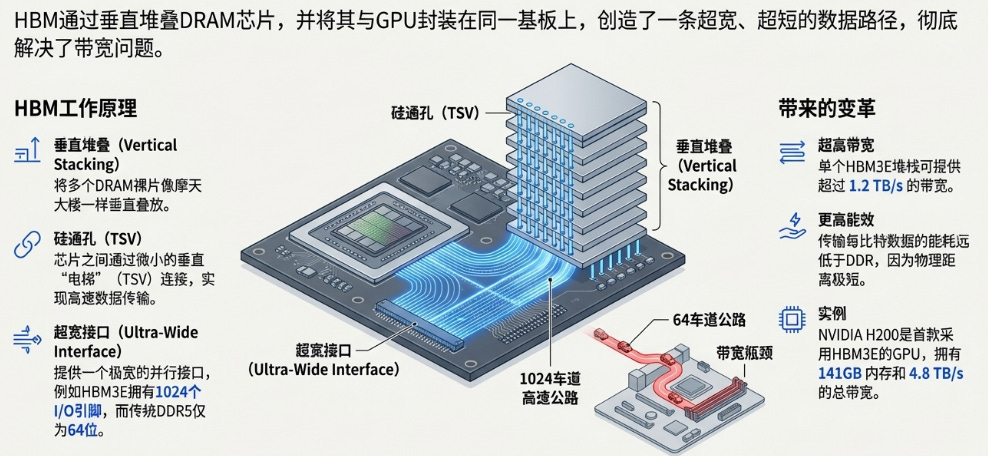

高带宽内存 (HBM):通过3D堆叠技术,将多个DRAM裸片垂直集成在计算芯片的封装基板上,提供超高带宽,是AI加速器的“工作内存”。

随着AI工作负载从训练到推理的不断演进,模型规模和数据吞吐量持续攀升,对内存系统的要求也日益严苛。因此,内存技术的创新(无论是提升带宽、增加容量还是优化功耗)都已不再是简单的工程细节,而是决定下一代AI系统性能上限和总体拥有成本的核心驱动力。下文将深入剖析正在重塑市场格局的关键技术转型。

2.0 关键技术转型及其市场影响评估

本节将深入探讨当前塑造AI硬件格局的三大关键内存技术转型:

高带宽内存(HBM)的演进

传统服务器内存的带宽突破(MRDIMM)

新兴的内存扩展技术(CXL)

我们将逐一评估这些技术对供应链、竞争动态及市场价值链的战略性影响。

2.1 HBM:从带宽引擎到半定制组件的演变

HBM技术通过垂直堆叠多个DRAM裸片,并采用一个极宽的并行接口(通过基底裸片和高密度互连实现),从根本上解决了传统DDR内存面临的带宽瓶颈。其核心优势在于,相较于在长距离电路板走线上提升信号速率,HBM通过缩短物理距离和扩大接口宽度,实现了无与伦比的每瓦带宽和每封装面积带宽,这对于功耗和空间受限的AI加速器至关重要。

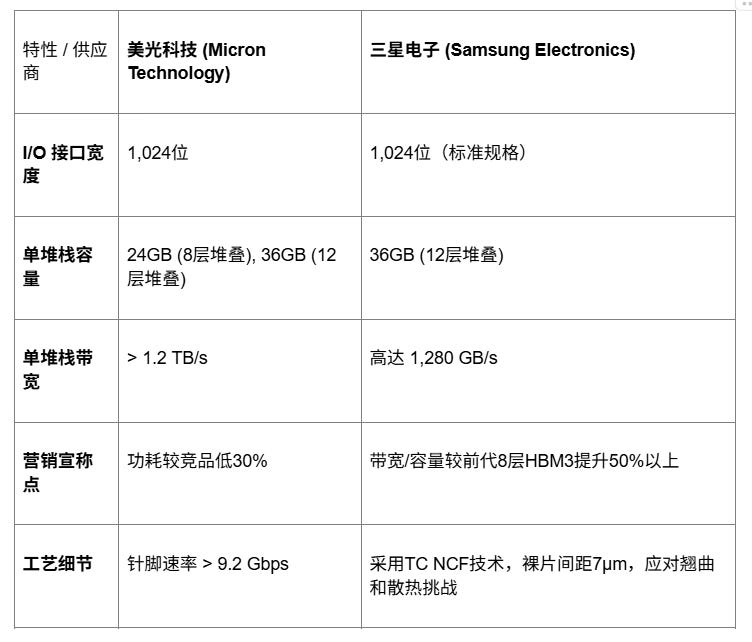

供应商发布的产品规格凸显了HBM的技术特性和竞争焦点。以下是美光与三星近期HBM3E产品的对比:

注:美光关于功耗优势的声明,应被视为方向性的营销数据,而非经过独立验证的基准测试结果。

这些技术细节清晰地表明,HBM的竞争已超越了单纯的内存产品范畴,演变为一场先进封装工艺的综合挑战。随着堆叠层数从8层向12层甚至更高发展,良率控制、芯片翘曲、热量耗散以及机械公差等封装层面的问题,已成为决定成本和可交付供应量的一级驱动因素。

展望未来,从HBM3E到HBM4的技术跃迁将带来更深远的战略影响。HBM4标准的核心特征包括将接口宽度翻倍至2048位,以及引入客户可定制化的基底逻辑裸片(base die)。这一变化意义重大:它使得HBM不再是可被轻易替换的标准化商品。客户(如NVIDIA)可以与内存供应商共同设计基底裸片,以优化特定功能。这将显著降低不同供应商产品间的可互换性,从而增加客户的转换成本,并可能将市场竞争从现货价格博弈转向基于长期设计合作的半定制模式。

2.2 传统服务器内存:主机端带宽的突破

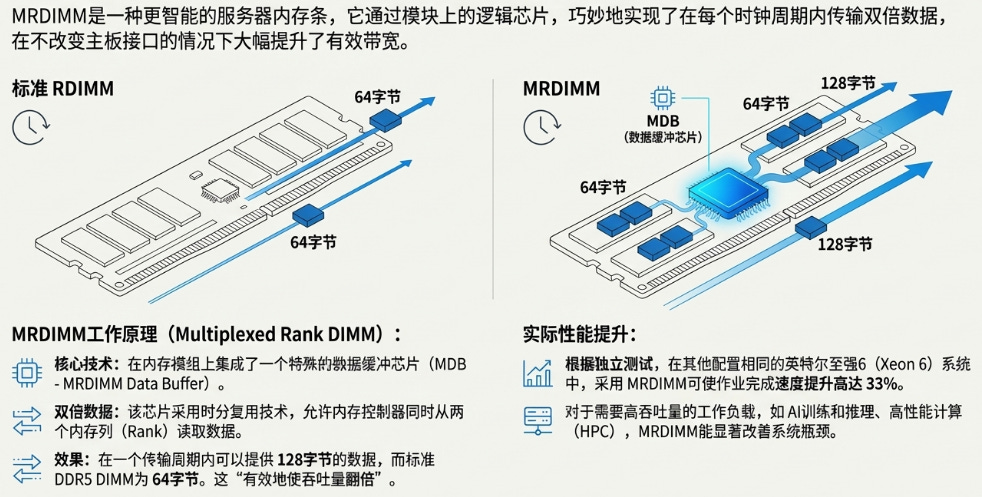

随着服务器CPU核心数量的不断增加,每个核心可分配到的内存带宽却在相对下降,这一矛盾限制了数据预处理、内存数据库以及其他CPU密集型AI工作负载的性能。多路复用秩双列直插内存模组(MRDIMM)技术正是应对此挑战的一项务实解决方案。

MRDIMM技术的核心工作原理及其生态价值可归纳如下:

工作原理:MRDIMM在与现有RDIMM相同的接口和外形尺寸下,通过在模组上集成缓冲和多路复用逻辑芯片(如Montage的MRCD/MDB芯片),实现了对两个内存秩(rank)的同时操作。这种机制能够在一个时钟周期内传输128字节数据,而标准DDR5 DIMM只能传输64字节,从而“有效倍增”了吞吐量。

生态系统价值:

英特尔 (Intel) 将其定位为Xeon 6等新平台的低摩擦升级路径,根据其引用的独立测试,该技术可将作业完成速度提升高达33%。

Montage Technology 作为核心缓冲芯片供应商,其MRCD/MDB芯片是实现该架构的关键。

Cadence 等IP供应商则通过提供经过硬件验证的12.8Gbps IP核,加速了该技术的生态系统部署。

然而,需要注意的是,根据美光的披露,JEDEC的MRDIMM标准尚未最终发布。这意味着市场目前仍处于早期采用阶段,平台认证和跨厂商的互操作性仍在发展中,这对于寻求大规模部署的企业而言是一个需要关注的变量。

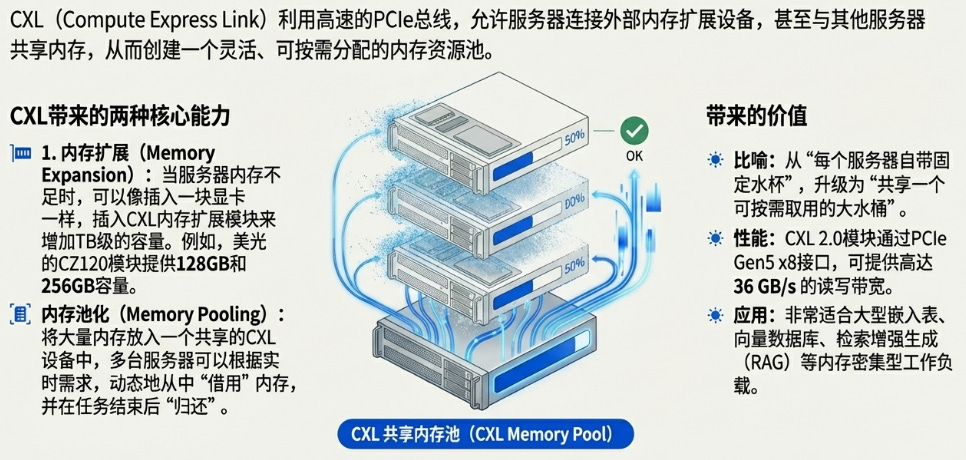

2.3 新兴内存层级:CXL与内存池化机遇

CXL(Compute Express Link)是一种基于PCIe物理层的高速互联标准,它为服务器内存系统引入了一个全新的扩展维度。CXL的定位并非要取代DDR作为主内存,而是作为一个补充性的容量层和资源池化层,以应对特定工作负载对海量内存的需求。

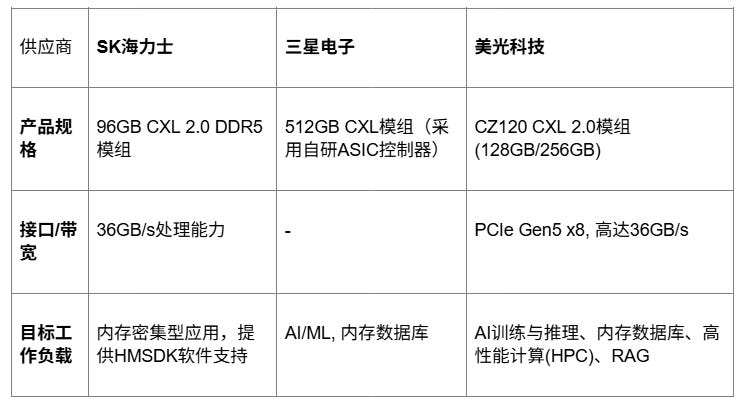

各大内存厂商正积极布局CXL产品,其规格和目标应用场景如下表所示:

综合来看,CXL旨在解决那些“容量比延迟更重要”的应用场景,例如大型嵌入表、向量数据库、检索增强生成(RAG)流程以及GPU旁的大规模数据预处理。CXL能否取得商业成功,关键在于其能否从当前的试点部署阶段发展到规模化应用。若能实现,它将为内存模组供应商及其上游的控制器、接口芯片厂商创造一个全新的增量市场。

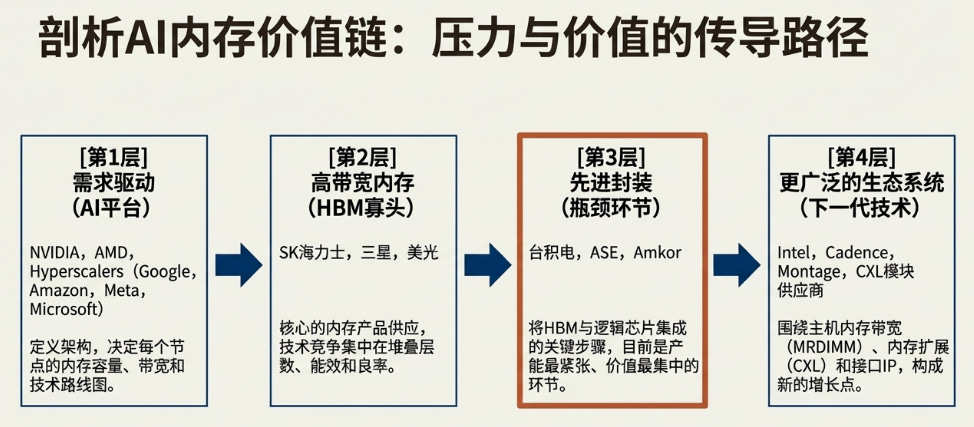

3.0 AI内存供应链:瓶颈、定价权与价值捕获

在千兆瓦级AI数据中心的宏大背景下,内存需求已从一个工程细节问题,上升为决定基础设施建设速度和规模的宏观约束。本节将剖析限制供应的关键瓶颈,并探讨这些瓶颈如何重塑价值链中的利润分配格局。

3.1 核心瓶颈:先进封装产能的决定性作用

当前,限制AI加速器出货量的最关键因素并非逻辑芯片的晶圆产量,而是先进封装的产能。

根据台积电(TSMC)和英伟达(NVIDIA)的声明,以CoWoS(Chip-on-Wafer-on-Substrate)为代表的2.5D/3D封装技术是当前AI硬件供应的决定性瓶颈。值得注意的是,据NVIDIA称,尽管先进封装产能相较不到两年前已增长了大约4倍,但它仍然是一个瓶颈。这凸显了需求增长的速度已经远远超过了大规模的供应响应。为应对井喷式的需求,TSMC正在积极扩产:

2024年:计划将CoWoS产量翻倍。

2025年及以后:计划进一步增加产能。

2027年:计划推出光罩尺寸达9.5倍的CoWoS技术,以能够集成12个HBM堆栈或更多。

这一瓶颈对市场产生了双重影响。一方面,它直接限制了像NVIDIA这样的下游计算供应商的短期收入上限。另一方面,这种稀缺性维持甚至增强了上游关键组件供应商的定价权,包括HBM堆栈、ABF基板以及TSMC自身的封装服务。

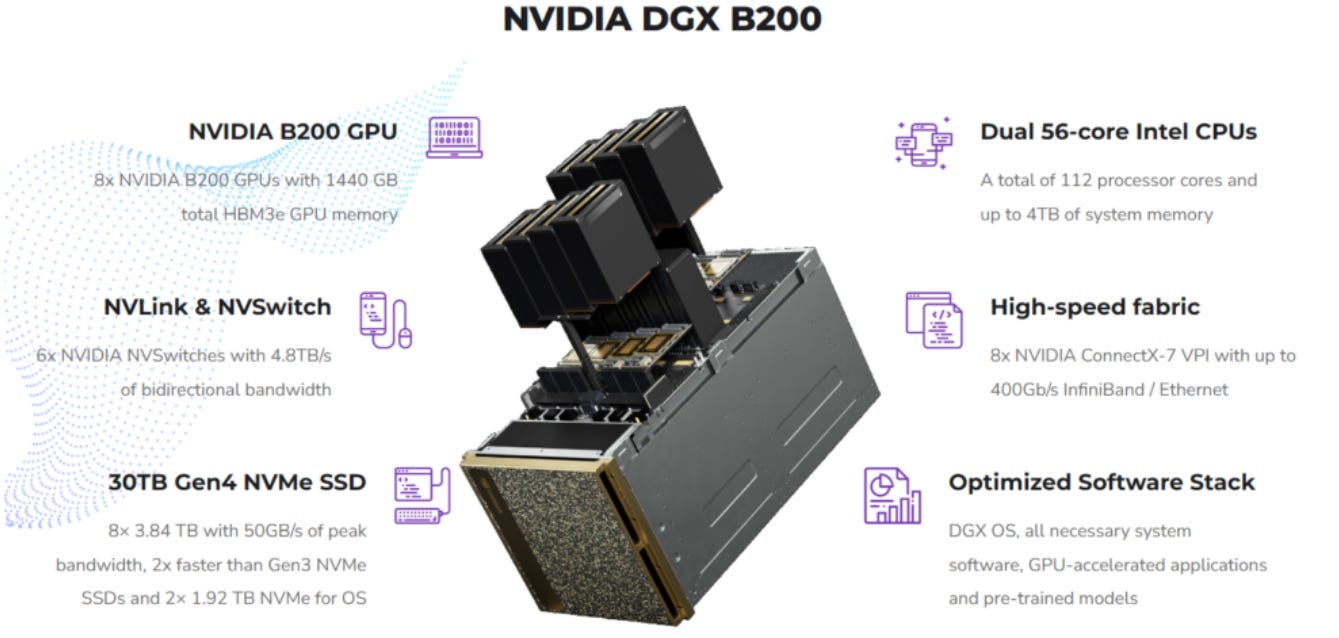

3.2 宏观供需:周期性与结构性增长的交织

AI平台对内存的需求量是惊人的。以NVIDIA的DGX B200系统(包含8颗Blackwell GPU,总计1,440GB HBM3e)为例进行估算,一个1GW(吉瓦)的IT负载数据中心,可能需要部署约7万套此类系统。这意味着仅这一个设施就需要消耗约100.7 PB(拍字节)的HBM,以及超过140 PB的主机内存。这一计算将HBM从一个组件转变为与设施电力和冷却基础设施同等重要的战略资源。

市场数据也印证了这一结构性转变。根据Gartner和TrendForce的预测:

2025年,HBM收入预计将达到210亿美元,同比增长70%。

届时,HBM将占到整个DRAM市场总收入的约18%,尽管其在比特总量中的占比要小得多,这反映了其极高的平均售价(ASP)和价值密度。

面对如此强劲的需求,供应商的资本支出策略也发生了显著变化。美光、SK海力士和三星的投资重点正普遍从单纯的产能扩张,转向工艺升级、高层数堆叠技术和高附加值产品(如HBM)。这种审慎的“资本纪律”有助于避免盲目扩产导致的供过于求,可能会延长行业的上升周期。然而,这也增加了执行风险,因为高附加值产品的最终产出高度依赖于TSV(硅通孔)堆叠和先进封装等复杂工艺的良率。

在当前这个由需求拉动和瓶颈限制共同定义的市场中,产业链上各参与者的战略定位直接决定了其盈利能力和市场地位。下一节将对关键参与者的竞争格局进行详细剖析。

4.0 竞争格局与关键参与者战略定位

本节将对AI内存生态系统中的关键公司进行深入的战略评估,分析它们在当前市场格局下的优势、劣势和核心战略。

4.1 需求定义者:平台架构的引领者

英伟达 (NVIDIA):作为当前HBM需求的核心“消费引擎”,NVIDIA的地位举足轻重。其平台路线图(如从H200到Blackwell架构)直接定义了HBM的技术规格(如容量、带宽)和迭代节奏,为整个内存供应链设定了明确的目标和时间表。

AMD 与 英特尔 (Intel):

AMD 是HBM的另一个重要需求来源,其MI300系列加速器同样集成了高容量HBM,为内存供应商提供了关键的客户多元化选择。

英特尔 则主要通过其服务器平台标准来影响主机内存市场。它对MRDIMM等新技术的推动,直接塑造了DDR5内存模组及其配套芯片的市场需求。

4.2 HBM寡头:技术、份额与利润的博弈

SK海力士 (SK hynix):凭借其先发优势,SK海力士被定位为当前HBM市场的领导者。分析师预计其2025年市场份额约为66%。其领先地位的核心驱动力在于卓越的技术执行力,包括在HBM4开发上的领先进度,以及成熟的MR-MUF封装工艺。正如2.1节所讨论的,HBM4向客户定制化基底裸片的转变,将通过降低供应商之间的可互换性来增强其领导地位,从而增加客户的转换成本。

三星电子 (Samsung Electronics):作为规模庞大的追赶者,三星的战略核心在于利用其强大的制造能力来缩小与领先者的差距,但其HBM执行风险与规模优势之间存在一定的张力。三星推出的HBM3E 12H产品,及其在TC NCF等先进工艺上的投入,表明其正全力以赴地追赶技术前沿,以期夺回市场份额。

美光科技 (Micron Technology):作为美国唯一的主要DRAM供应商,美光拥有独特的战略地位,并在HBM市场展现出强劲的份额增长潜力。其HBM3E产品已成功进入NVIDIA H200供应链,证明了其技术竞争力。此外,美光在CXL和MRDIMM等新兴领域的积极布局,为其提供了超越HBM的多元化增长路径。

4.3 关键赋能者:产能瓶颈的掌控者

台积电 (TSMC):凭借其CoWoS技术,台积电在AI先进封装领域占据了准垄断地位。其产能扩张计划的节奏,直接决定了整个AI硬件市场的供应上限,其路线图也将为未来集成更多HBM堆栈铺平道路。

OSAT厂商 (如ASE、Amkor):在封装产能极度紧张的背景下,传统封测代工厂(OSAT)迎来了重要机遇。它们不仅能够承接来自TSMC的产能溢出,也成为客户寻求供应链多元化和地缘政治风险对冲的关键合作伙伴,例如NVIDIA计划与Amkor合作以扩大在美国的制造能力。

4.4 周边生态系统:价值链的“镐与铲”

AI内存的复杂性提升,催生了一批提供关键工具和组件的“镐与铲”供应商,它们的价值捕获来自于行业技术难度的增加,而非单纯的内存比特量增长。

接口IP/EDA供应商 (Cadence, Synopsys):随着内存接口速率和复杂度的提升,它们提供的IP核与验证工具成为芯片设计公司不可或缺的资产。

内存模组缓冲芯片供应商 (Montage Technology):MRDIMM等新标准的出现,直接为其在内存模组上的缓冲芯片创造了新的增量市场。

半导体设备商 (ASML, Applied Materials, KLA, Besi):无论是DRAM的工艺节点演进,还是HBM的TSV蚀刻、晶圆键合与检测,都离不开这些设备商提供的精密工具,它们是整个产业升级的基石。

总而言之,AI内存的竞争已演化为一场跨越多个价值捕获层级的系统性竞争,包括(1)内存裸片制造,(2)堆叠与晶圆级封装,(3)HBM与逻辑芯片的2.5D/3D集成,以及(4)模组级集成。每个参与者的成功都与其他环节紧密相连,这为我们理解该领域的投资机会提供了关键视角。

5.0 投资论点与前景展望

本备忘录的最后一部分将综合以上分析,提炼出AI内存领域的核心投资论点、正反方观点,并指出投资者在未来应密切关注的关键变量,以做出明智的决策。

5.1 核心看涨情景 (Bull Case)

该领域的核心看涨逻辑建立在三个相互强化的支柱之上:

持续的AI资本支出:由大型语言模型驱动的AI基础设施建设浪潮预计将持续数年,为内存需求提供强劲的宏观支撑。

每个计算节点的内存密度提升:无论是HBM还是主机内存,每个AI加速器节点所需的内存容量和带宽都在迅速增长,驱动了“量价齐升”的局面。

供应紧张导致利润率走高:制造工艺的复杂性(尤其是先进封装)和供应商审慎的资本支出纪律共同导致供应紧张,这使得HBM和DRAM的利润率能够维持在高位。

5.2 核心看跌情景 (Bear Case)

核心看跌风险同样不容忽视,主要包括:

AI资本支出放缓:如果AI应用的投资回报率不及预期或宏观经济恶化,可能导致云服务商削减资本支出。

架构效率提升:软件和硬件的优化,如更激进的模型量化或稀疏化技术,可能会降低单位算力对HBM带宽和容量的依赖。

供应集中响应:如果各大供应商的产能扩张(包括封装和HBM)和良率提升在同一时间窗口内集中兑现,市场可能迅速从供应短缺转向供过于求。

5.3 市场认知偏差与关键问题 (Variant Perceptions)

当前市场参与者对以下三个核心问题的看法存在分歧,这些分歧点构成了潜在的投资机会:

HBM4引入的客户定制化基底裸片,能否显著提高转换成本,从而使其利润率在整个周期内维持类似特殊化学品的高位?

新兴的内存标准,如串行HBM(serialized HBM)和基于LPDDR的服务器模组,究竟是扩大了内存市场的总体规模,还是主要在现有内存类别内部产生替代压力?

CXL技术能否成功地从当前的试点部署阶段发展到规模化的生产应用,从而为相关模组和控制器供应商创造一个有意义的增量市场?

5.4 投资者关键监测指标

为了有效判断行业趋势并验证投资逻辑,投资者应密切跟踪以下关键变量:

HBM供应商验证状态:各大内存厂商在关键AI平台上的产品验证进度和量产供货时间表。

CoWoS产能与分配:TSMC及其他厂商的CoWoS产能扩张速度,以及这些产能如何在各大客户之间进行分配。

ABF基板交付周期:作为先进封装的关键材料,其交付周期是反映供应链紧张程度的先行指标。

DRAM库存与合同价格:DRAM制造商的库存周数,以及DDR4、DDR5和HBM的合同价格走势。

超大规模数据中心资本支出:头部云服务商发布的资本支出指引及其增长趋势。

注:

DDR(Double Data Rate,双倍数据速率)

MRDIMM(Multiplexed Rank DIMM,多路复用Rank DIMM)

HBM(High Bandwidth Memory,高带宽内存)

TSV(Through Silicon Via,硅通孔)

DRAM(Dynamic RAM,动态随机存取存储器)

SRAM(Static RAM,静态随机存取存储器)